ASML prevede un'ampia applicazione della tecnologia High‑NA EUV già l’anno prossimo per la produzione di chip con dimensioni dei transistor pari a 1,4 nm o inferiori.

Breve riassunto

Il nuovo stadio di miniaturizzazione dei circuiti richiede l’adozione di metodi di litografia più avanzati. Nei prossimi due anni il settore dovrebbe avviare la produzione di chip con apparecchiature High‑NA EUV, che consentono dimensioni fino a 8 nm in un singolo passaggio e aprono la strada a processi tecnologici da 1,4 nm e meno di 10 nm (DRAM).

1. Capacità tecnologiche di High‑NA EUV

Parametro | Valore

Apertura numerica (NA) | 0,55

Dimensione minima in un passaggio | ≤ 8 nm

Processi tecnici possibili | 1,4 nm (circuiti integrati), < 10 nm (DRAM)

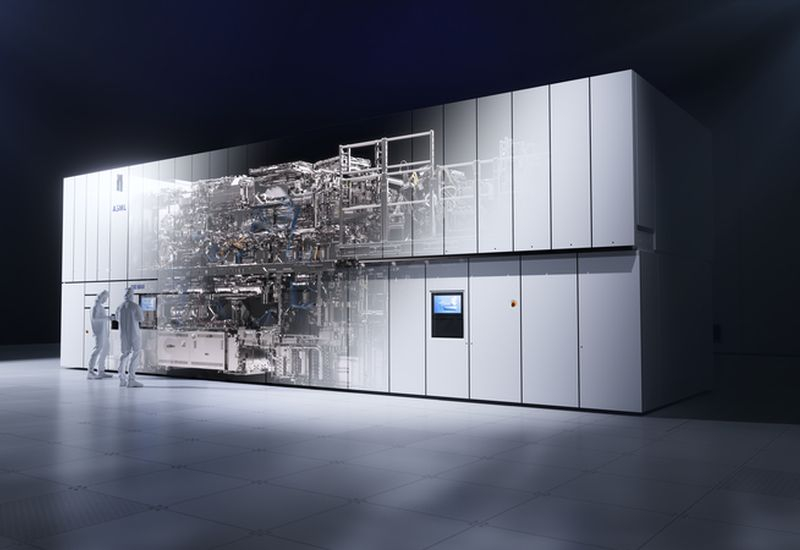

Queste caratteristiche rendono l’attrezzatura ASML Twinscan EXE:5200B e soluzioni analoghe critiche per le future tecnologie microelettrotroniche.

2. Attori chiave

Azienda | Stato di implementazione | Commento

ASML | Produttore High‑NA EUV | I primi clienti: Intel, Samsung, SK Hynix

TSMC | Non pronto all’uso massivo | Costo di un sistema – 380 mio USD; previsto ritiro dei chip da 1,4 nm

Intel | Dicembre 2023 ha introdotto Twinscan EXE:5200B | Preparazione per la tecnologia 14A e attrezzature correlate

Samsung Electronics | Ha ricevuto il primo scanner a dicembre 2023; secondo nel semestre corrente | Intende usarlo per Exynos 2600 (2 nm) e futuri processori Tesla

SK Hynix | Adotta High‑NA EUV da settembre 2023 | Usa già EUV tradizionale in DRAM (10 nm), prevede almeno cinque strati EUV per la sesta generazione

Micron Technology | Non ha ancora definito le tempistiche di implementazione | Possibili piani per High‑NA EUV

Rapidus (Giappone) | Adotta tecnologia 2 nm; mira al 1,4 nm nel 2029 | Nel 2027 dovrebbe avviare la produzione massiva di chip da 2 nm in Hokkaido

3. Aspetti economici

* Il costo dell’attrezzatura – un sistema High‑NA EUV costa circa 380 mio USD.

* L’adozione di apparecchiature più costose aumenta il costo di produzione, che alla fine si riflette sui consumatori.

* Perciò i grandi produttori (TSMC, Rapidus) mostrano cautela e pianificano l’introduzione in modo graduale.

4. Tempi previsti

I nuovi scanner litografici ASML per la produzione massiva di semiconduttori avanzati inizieranno a essere utilizzati attivamente tra il 2027 e il 2028. Fino ad allora le aziende regoleranno progressivamente le proprie linee produttive, integrando High‑NA EUV nei processi tecnologici esistenti.

Conclusione

La transizione a High‑NA EUV è un passo chiave per raggiungere dimensioni fino a 1,4 nm e DRAM più compatti. I principali attori mondiali hanno già iniziato i lavori preparatori, ma l’implementazione massiva è prevista solo tra qualche anno a causa dei costi elevati e della necessità di adattare le catene produttive.

Asted Cloud

Asted Cloud

Commenti (0)

Condividi la tua opinione — per favore, sii cortese e resta in tema.

Accedi per commentare